Next in line in the awesome tutorial series from Nandland was VGA. I didn’t have a VGA connector for my FPGA, but wondered if I could jury-rig something with what I had on hand.

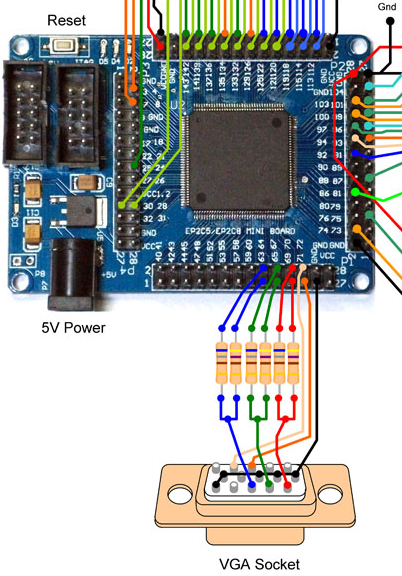

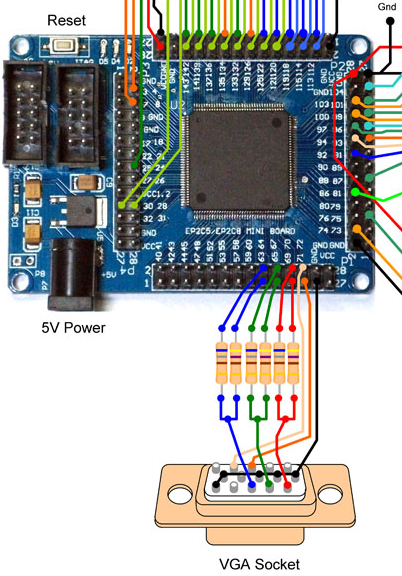

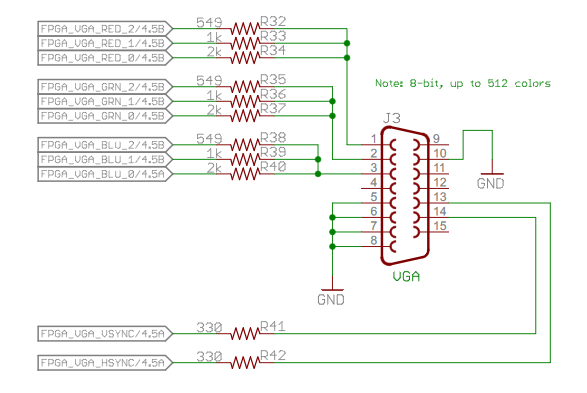

The wiring diagram below from Grant Seale’s Multicomp gave me a very good idea on how to go about it.

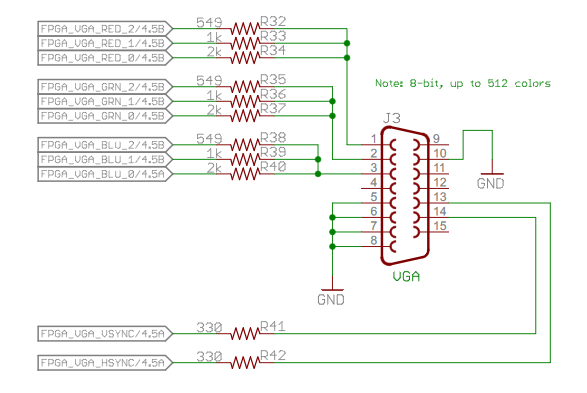

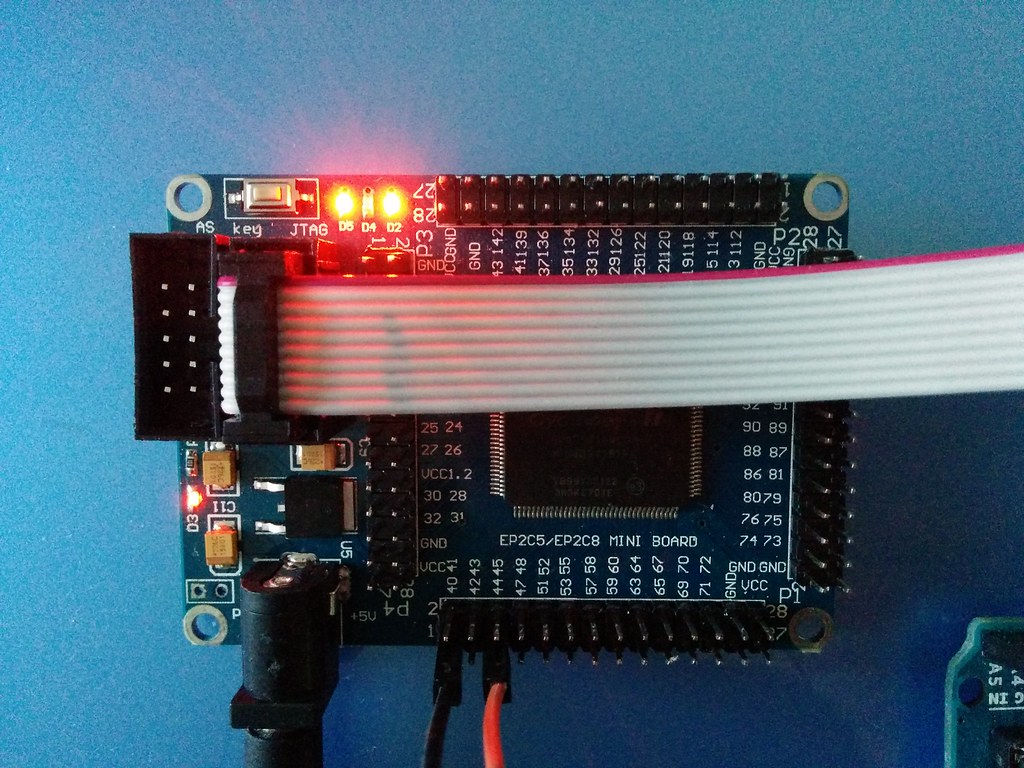

In the Nandland tutorial (image below), three signals are used per channel instead of two so my setup reflects that.

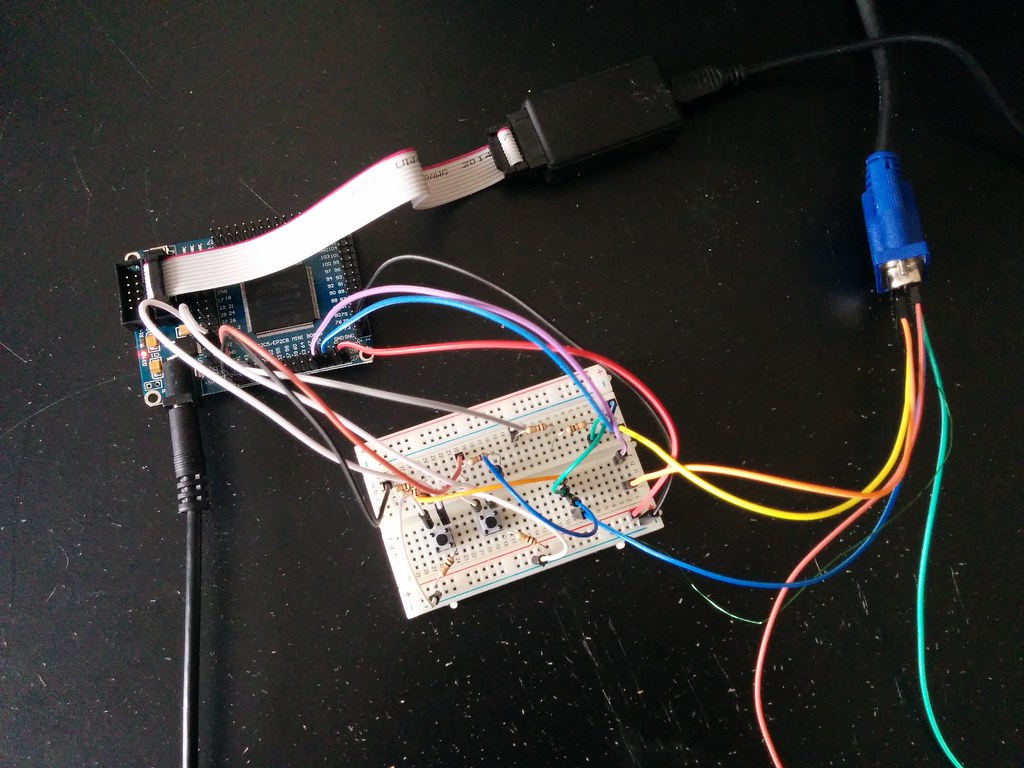

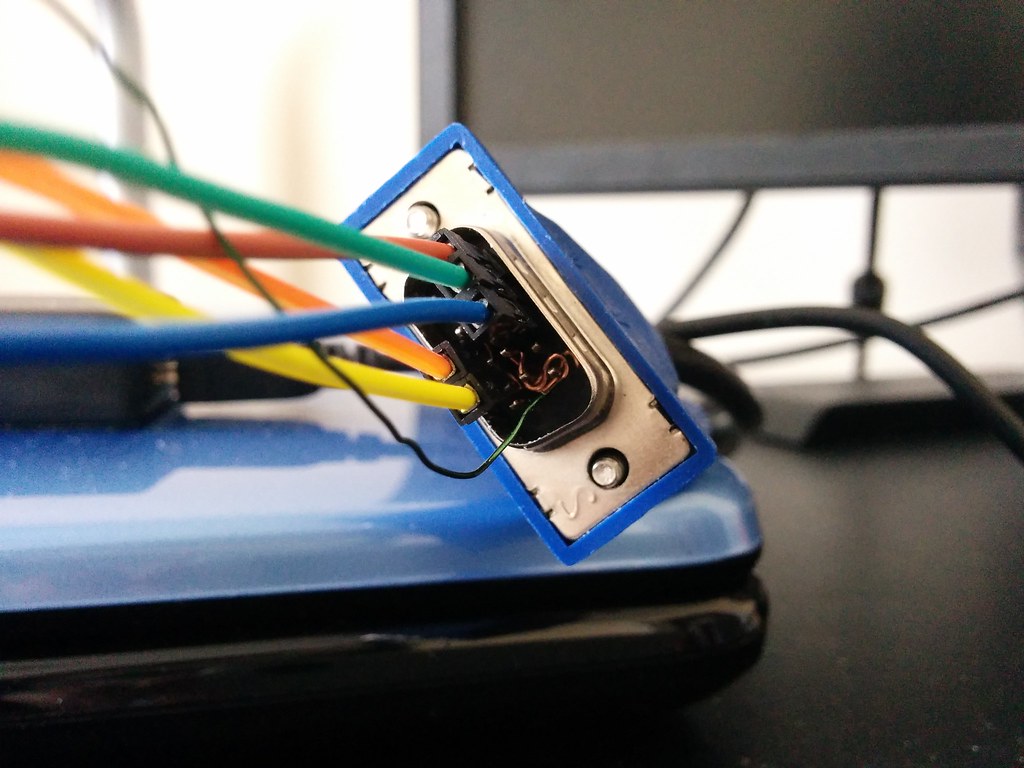

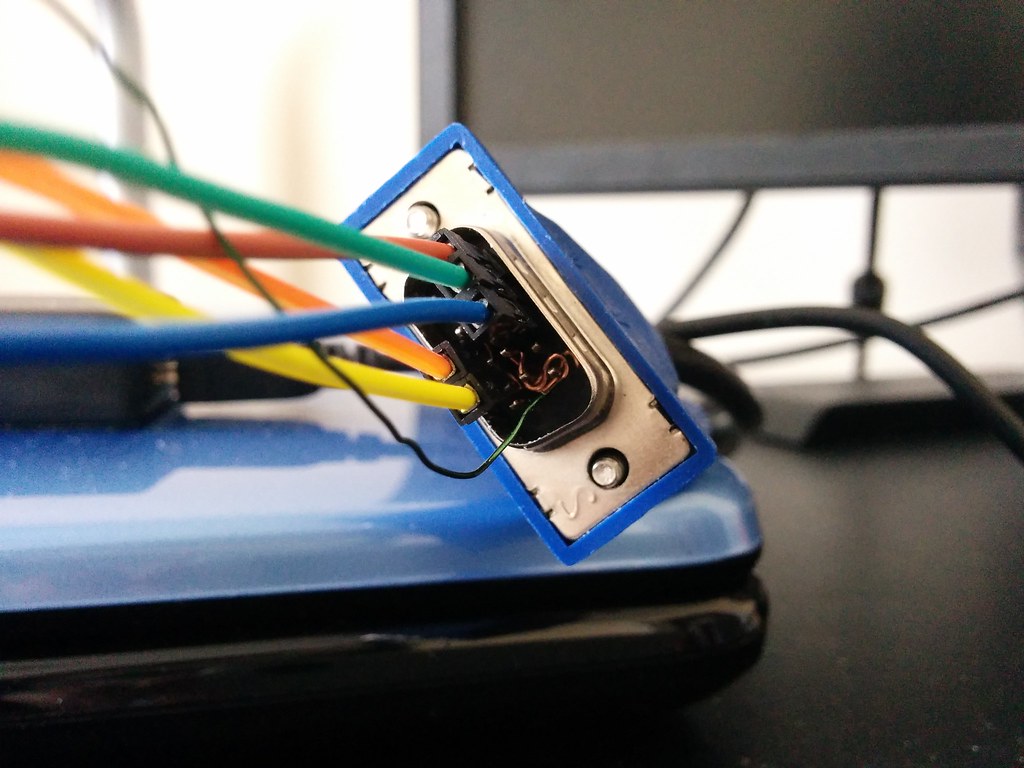

I had five 1Kohm resistors on hand, enough to control one channel. I used two of them in parallel to get the 500 ohms (close enough to 549), two in series to get the 2K ohms, and one on its own for the 1K ohms. Jumper wires were used to connect to the pins (red, green, blue, hsync, vsync). Luckily, all the ground pins were in-line (and the random pin in-between was an unused pin) so I just tied the whole line to ground using one wire (instead of several jumper wires). Here is the final masterpiece:

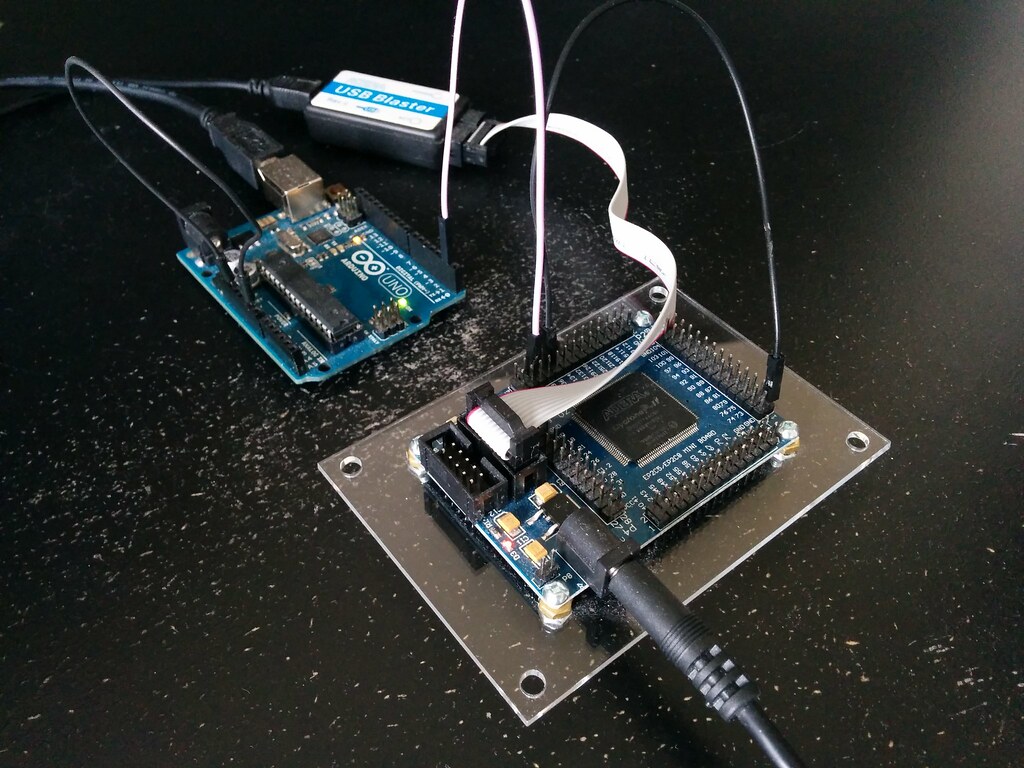

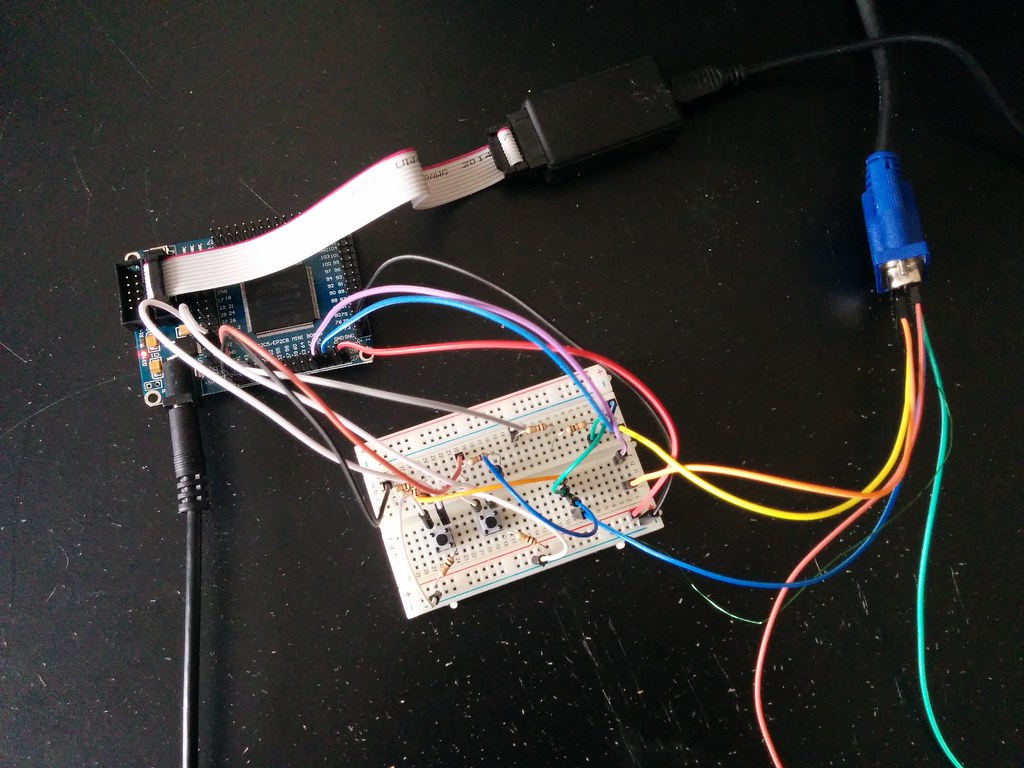

And the overall setup: